寒假报名了一生一芯的训练,作为对我这个学期的知识的一个补全,顺便学一些新的知识。为下个学期研究二进制安全做一点准备。这一部分就记录我在学习过程中的一些心得体会。就不再像往常一样讲的那么详细了,因为知识点在文档中给的很清楚,没必要再敲一遍。

通过晶体管实现0和1

主要认识两种类晶体管:

- nMOS:当G为高电压时,电信号由S->D;反之则阻塞信号

- pMOS:当G为低电压时,电信号由S->D;反之则阻塞信号

- 注意两者输入输出的方向,pMOS图带圈

通过晶体管搭建门电路

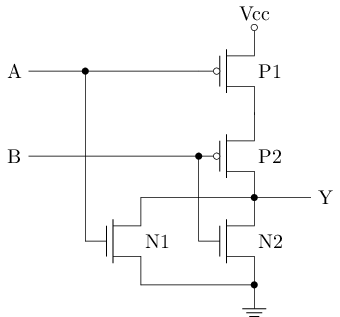

F3.2.1 分析门电路

尝试分析以下门电路的行为和功能.

基于mos管,我们可以实现基础的门电路,我们分析下面的门电路功能:

只有A和B均为低电压时,才能输出高电平信号。当A或B任一处于高电压时,输出低电平信号。分析为——NOR门

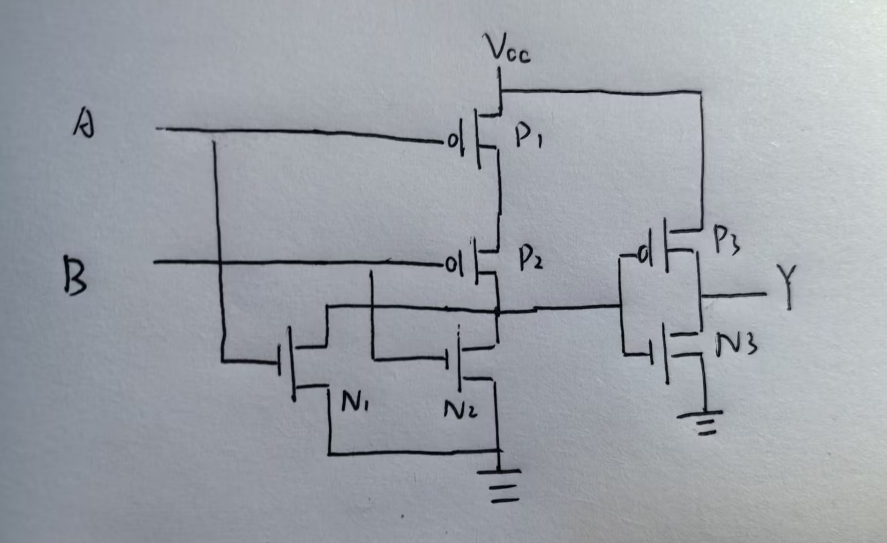

F3.2.2 或门的晶体管结构

尝试画出或门的晶体管结构.

画出或门的晶体管结构,就是在上面的基础上加上一个非门的晶体管结构就好了:

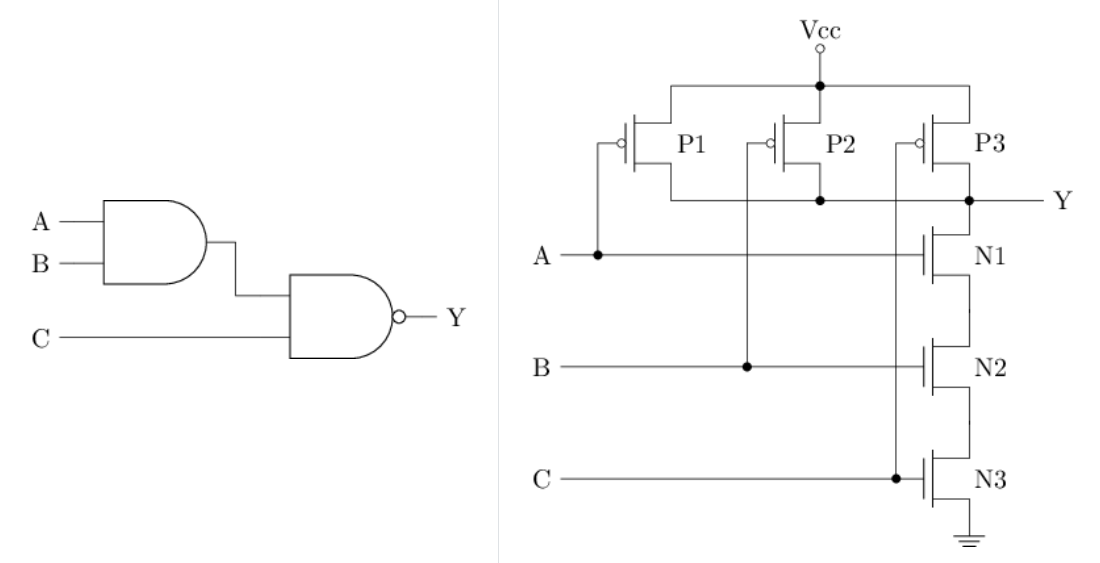

F3.2.3 对比两种实现的晶体管所需要的数量

不难分析, 上述晶体管结构同样实现了三输入与非门的功能. 尝试对比两种实现方式中所需晶体管的数量.

分别对两种方案进行计算:

1 | // 门电路方案 |

F3.3.1 用其他门电路搭建异或门

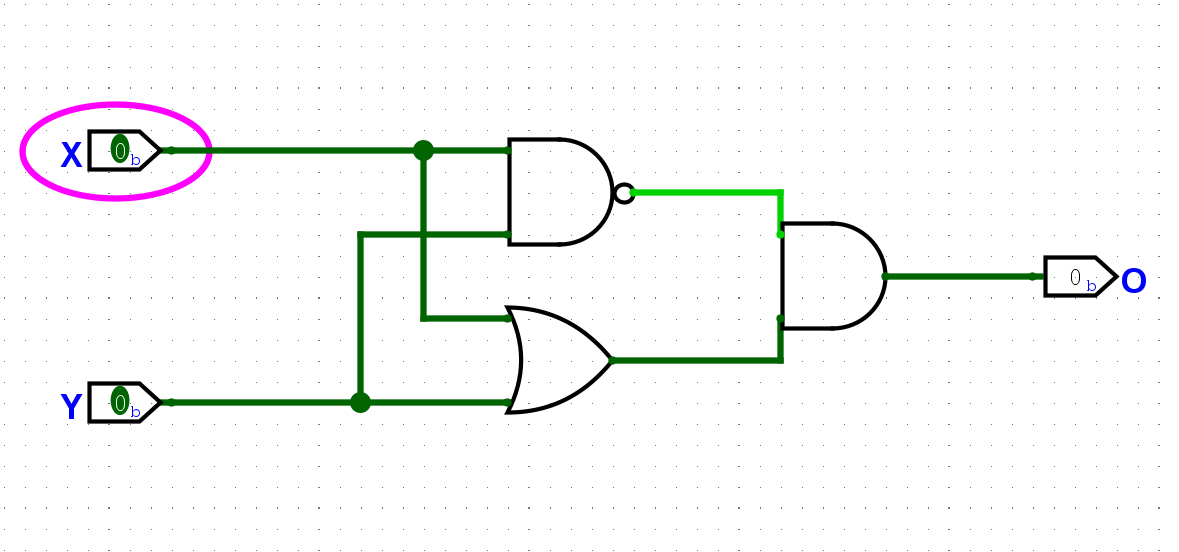

尝试在Logisim中用上文提到的门电路搭建一个异或门. 搭建后, 通过仿真检查你的方案是否正确.

实现正确后, 计算你的方案使用了多少个晶体管.

异或门的真值表,也可以看作是或门和与非门的交集。根据这个特征我们可以通过以下形式实现异或门:

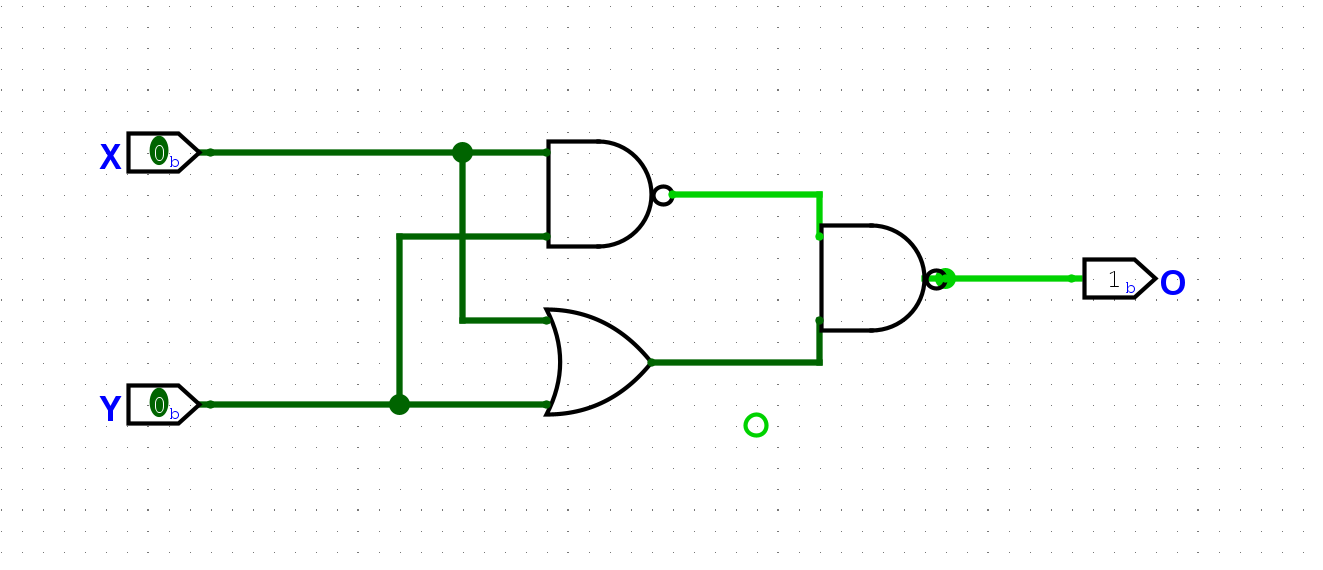

F3.3.2 设计同或门

还有另一种操作是”同或”操作, 当输入A和B相同时, 结果为

1, 否则为0. 同或操作可以认为是异或操作结果的取反.尝试在Logisim中用上文提到的门电路搭建一个同或门. 搭建后, 通过仿真检查你的方案是否正确.

在上面的基础上加一个非门就行了:

进位计数法

主要讲了2,10,16进制间的转换,这个比较简单,暂时略过。

通过门电路搭建基本组合逻辑电路

我们基于晶体管实现了门电路,现在我们将忽略晶体管的电气特性,将视角聚焦到门电路层面。在此基础之上,搭建各种基础的基础电路模块。

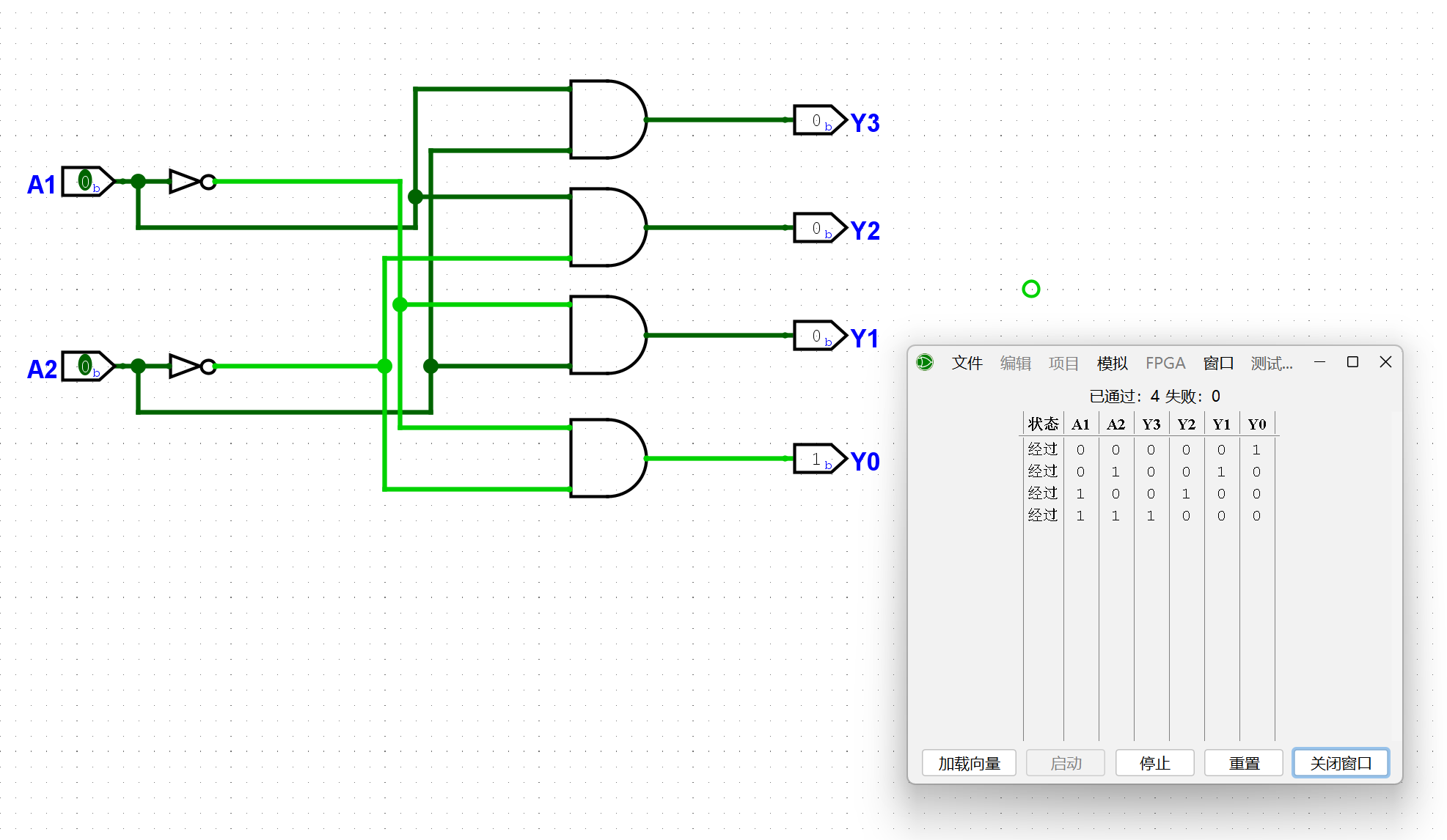

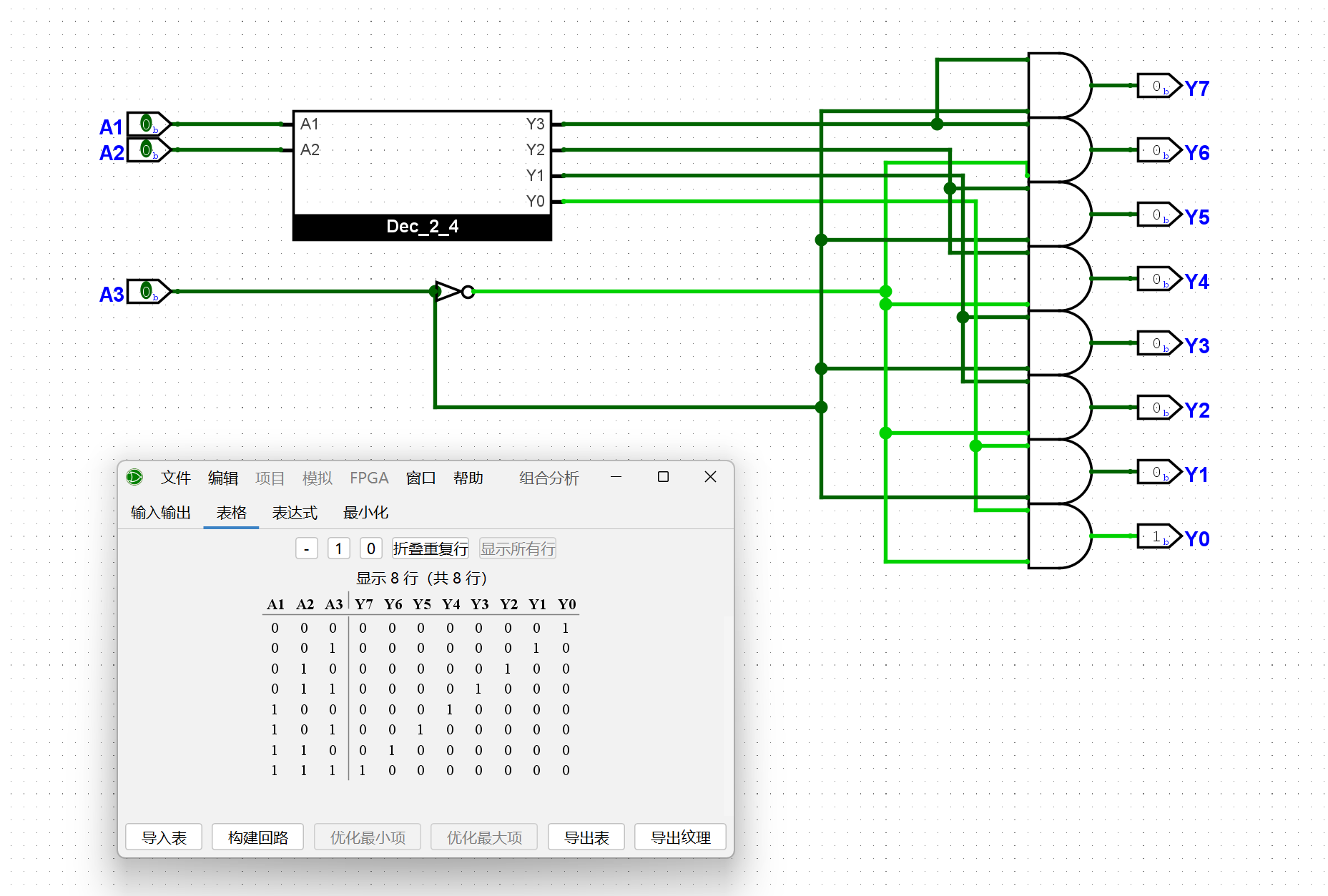

F3.5.1 搭建2-4译码器

尝试在Logisim中用门电路搭建一个2-4译码器, 它有2位输入, 4位输出. 搭建后, 通过仿真检查你的方案是否正确.

Logisim中也直接提供了译码器等现成的元件, 但我们还是要求大家使用门电路来搭建它们, 从而更好地学习数字电路的基本原理.

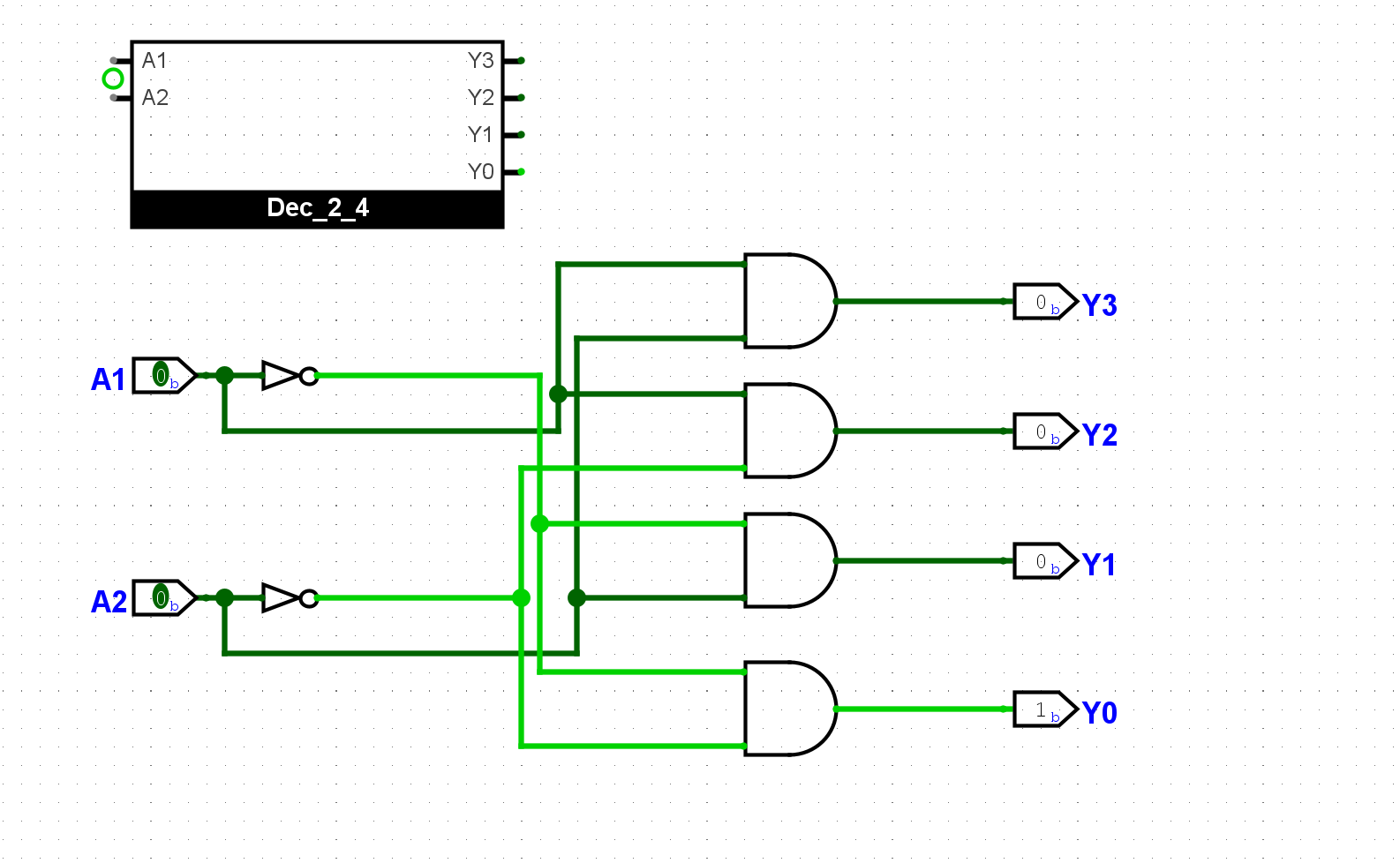

F3.5.2 Logisim中的子电路功能

译码器在后续的数字电路设计中会经常用到, 为了避免用户重复设计相同的电路, Logisim提供了子电路功能, 相应电路只需要设计一次, 后续即可反复实例化. 具体操作方式请阅读官方手册中的

Subcircuits(子电路)部分.学习如何使用Logisim的子电路功能后, 尝试将你设计的译码器封装成子电路.

可以通过添加电路,然后设置好IO引脚,这样就可以打包成一个子电路,方便之后调用:

F3.5.3 译码器的扩展

3-8译码器有3位输入, 8位输出. 尝试实例化若干个2-4译码器(具体数量交给你的思考), 并添加少量门电路, 从而实现3-8译码器的功能. 搭建后, 通过仿真检查你的方案是否正确.

通过第三个信号和原有的2-4译码器,实现3-8译码器

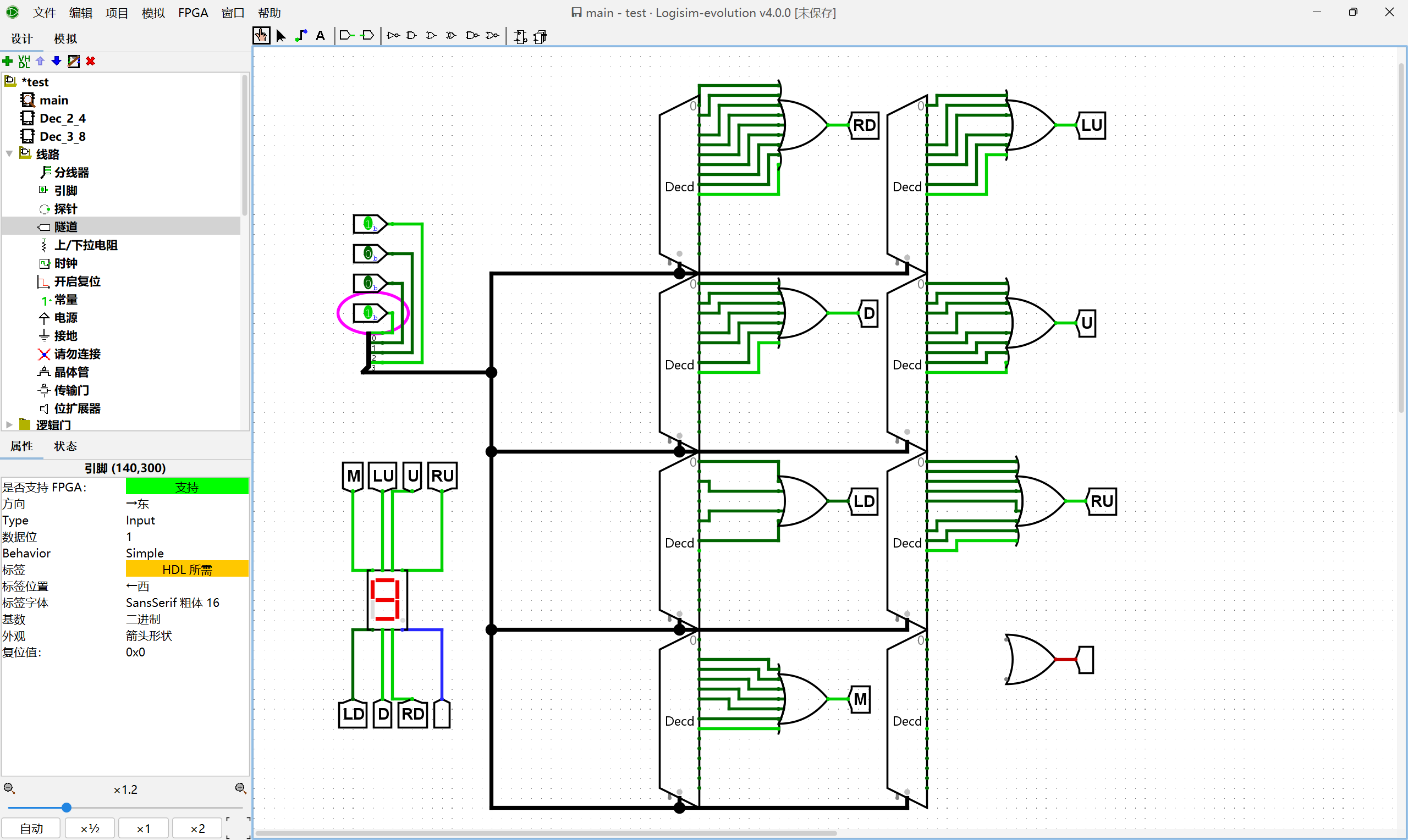

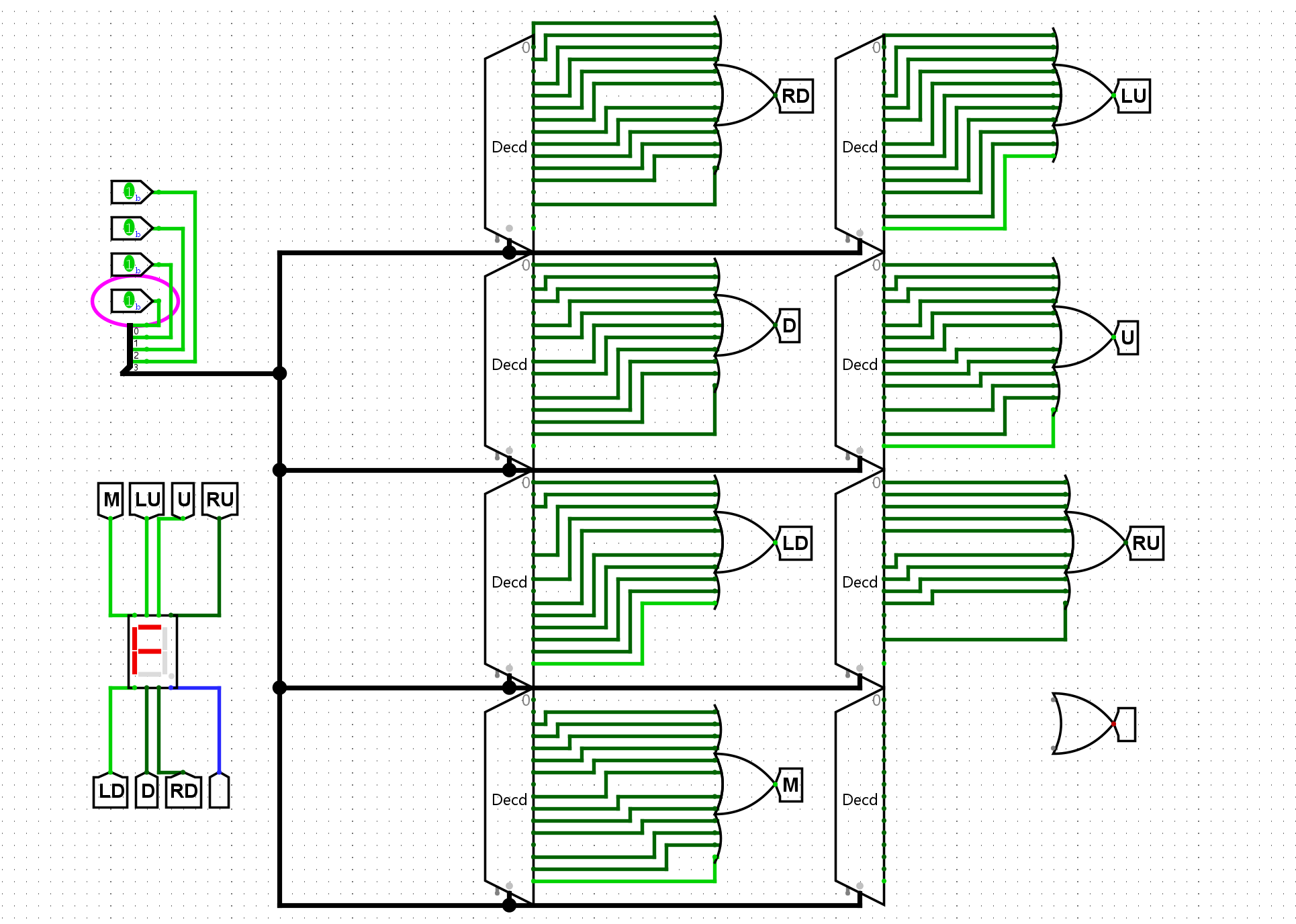

F3.5.4 搭建七段数码管译码器

尝试在Logisim中通过门电路搭建一个七段数码管译码器, 它有4位输入和8位输出, 分别与拨码开关和七段数码管相连. 七段数码管译码器支持十进制数字的显示, 即当输入对应0-9时, 七段数码管显示对应的数字; 对于其他输入, 七段数码管只显示小数点. 搭建后, 通过仿真检查你的实现是否正确.

这里用了隧道和解码器,来简化实现,对着文档搓就行了。RTFM!!!

F3.5.5 搭建七段数码管译码器(2)

尝试在Logisim中通过门电路搭建一个支持十六进制数字的七段数码管译码器. 和上述的十进制数字相比, 当输入对应10-15时, 七段数码管分别显示A, b, C, d, E, F. 搭建后, 通过仿真检查你的实现是否正确.

在上一个的基础之上添加对A,b,C,d,E,F的数码管支持就好了。就是有点麻烦。

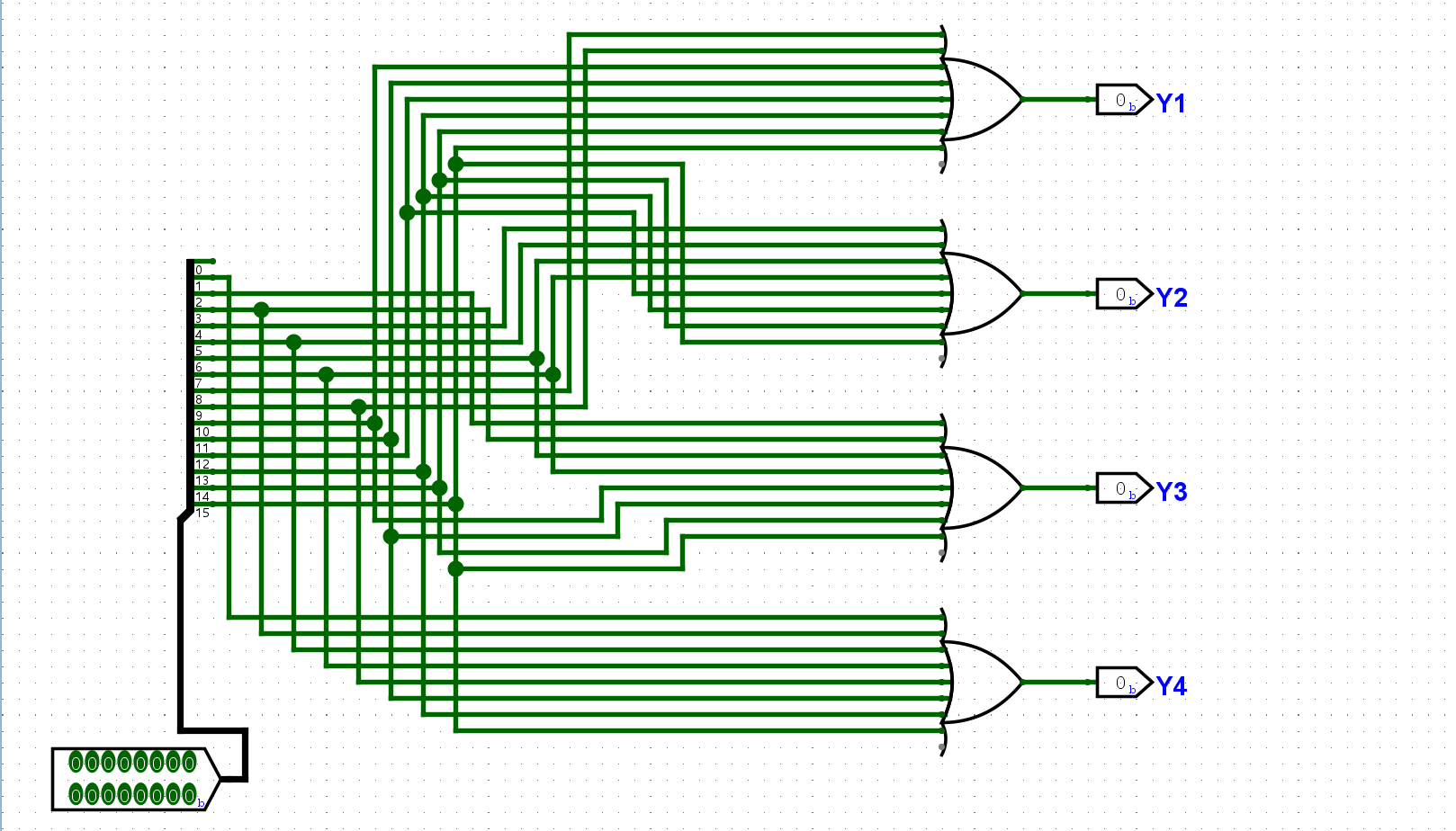

F3.5.6 编码器

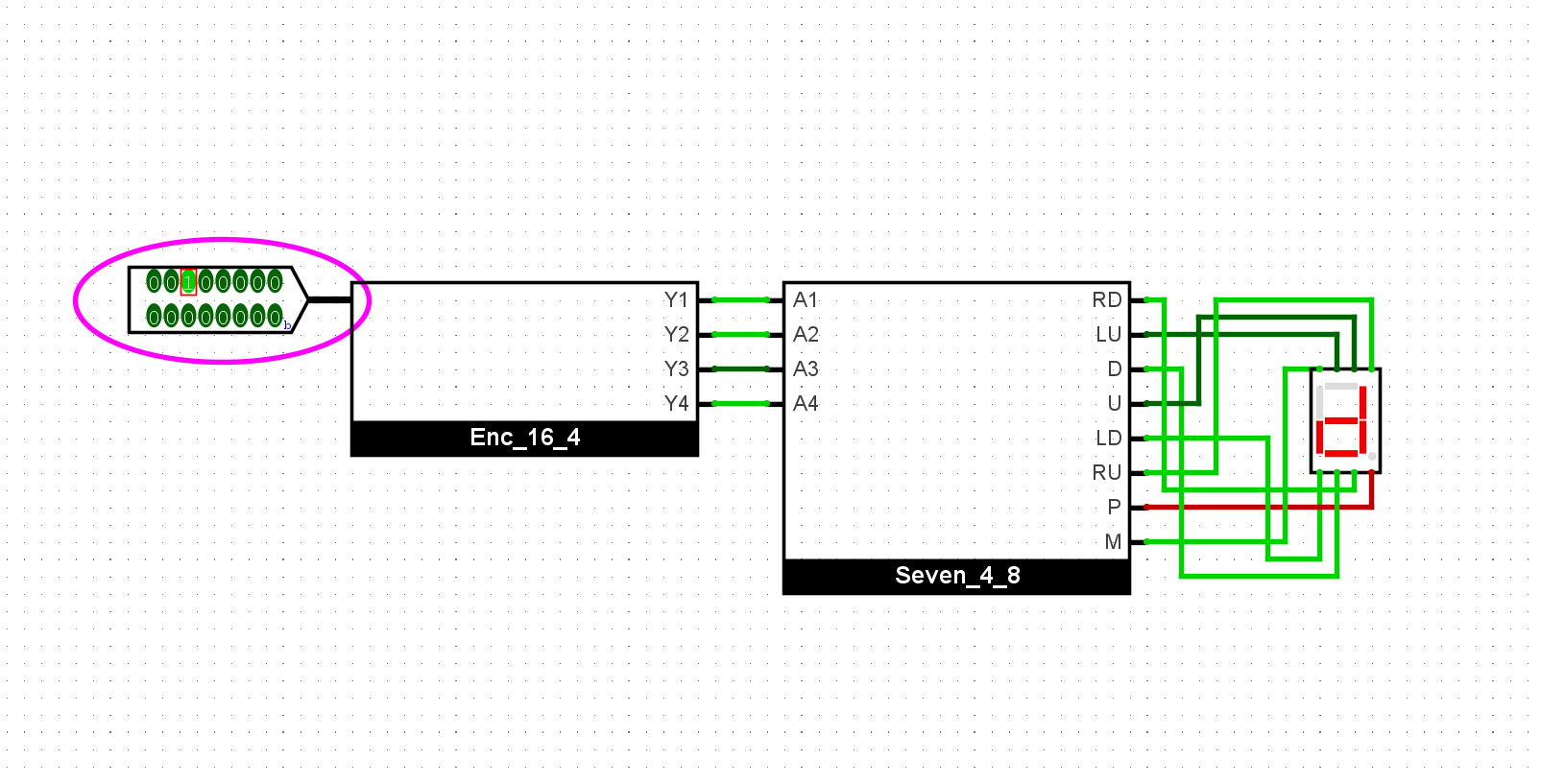

尝试在Logisim中通过门电路搭建一个16-4编码器, 它有16位输入和4位输出, 分别与拨码开关和七段数码管译码器相连, 使得编码器的输出结果通过十六进制数字显示在七段数码管中. 搭建后, 通过仿真检查你的实现是否正确.

每个Y的输出只关注当前的二进制对应的位数是否需要Y,然后使用或门进行合并:

使用封装的译码器驱动我们的七段管:

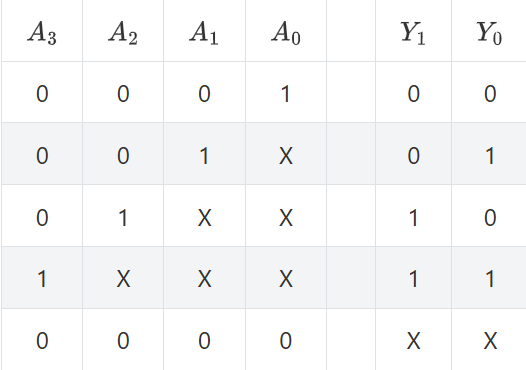

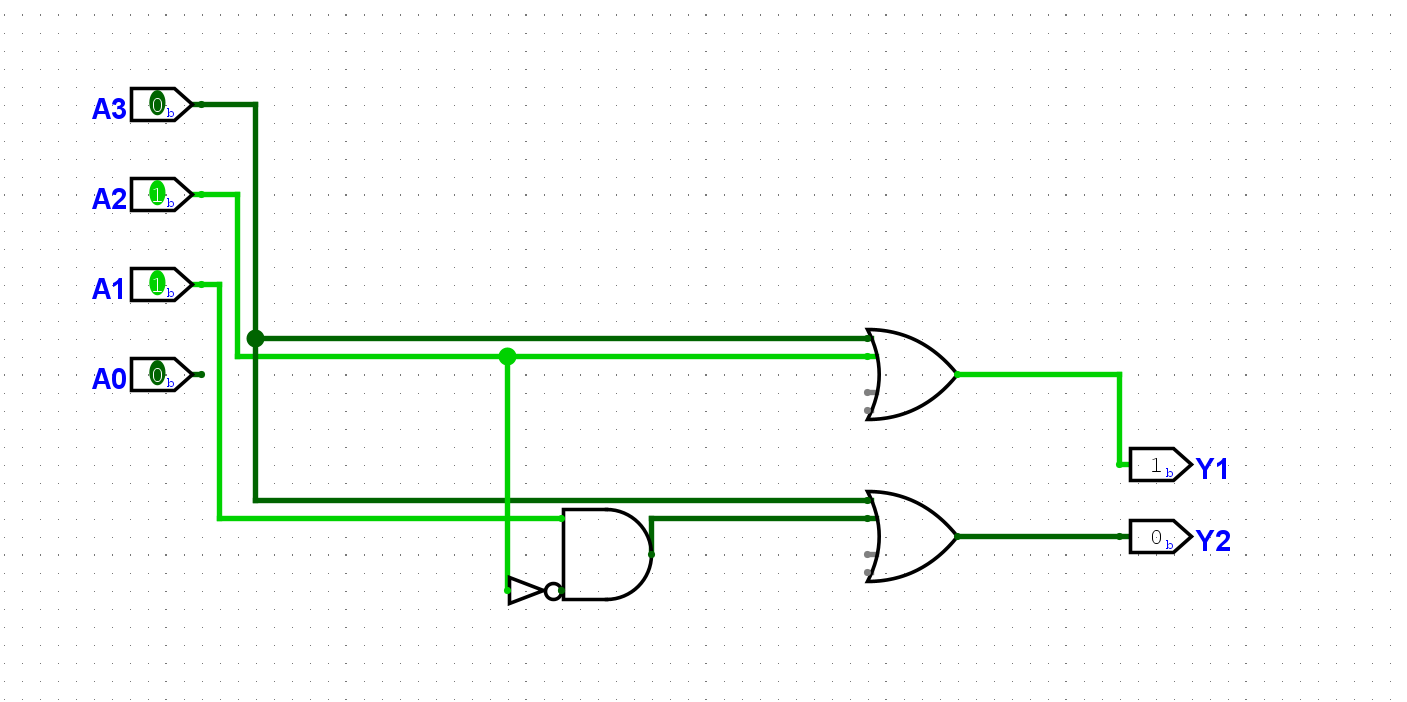

F3.5.7 搭建4-2优先编码器

根据上述真值表, 尝试列出每一位输出的逻辑表达式. 然后尝试在Logisim中通过门电路搭建一个4-2优先编码器. 搭建后, 通过仿真检查你的方案是否正确.

实现后, 对比4-2编码器和4-2优先编码器所需的门电路数量.

实现的过程中发现只有当A2为1时,后面的A1信号会对结果造成影响。设置一个与门作为开关就可以抑制这个现象了:

门电路数量比较:

1 | // 4-2 |

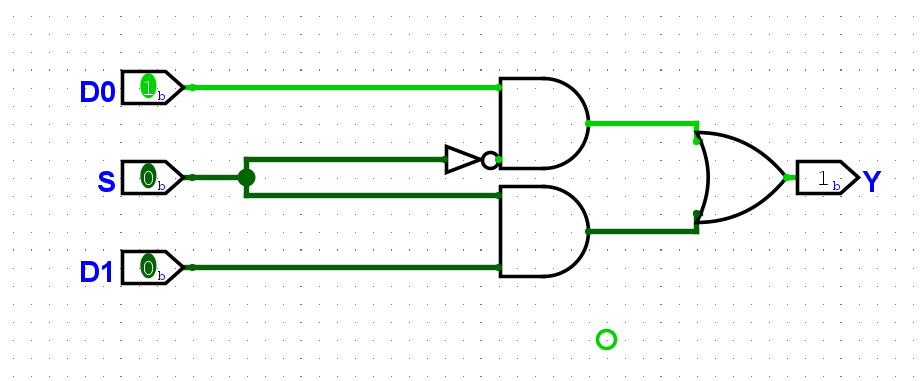

F3.5.10 搭建1位2选1选择器

尝试在Logisim中通过门电路搭建一个1位2选1选择器. 搭建后, 通过仿真检查你的方案是否正确.

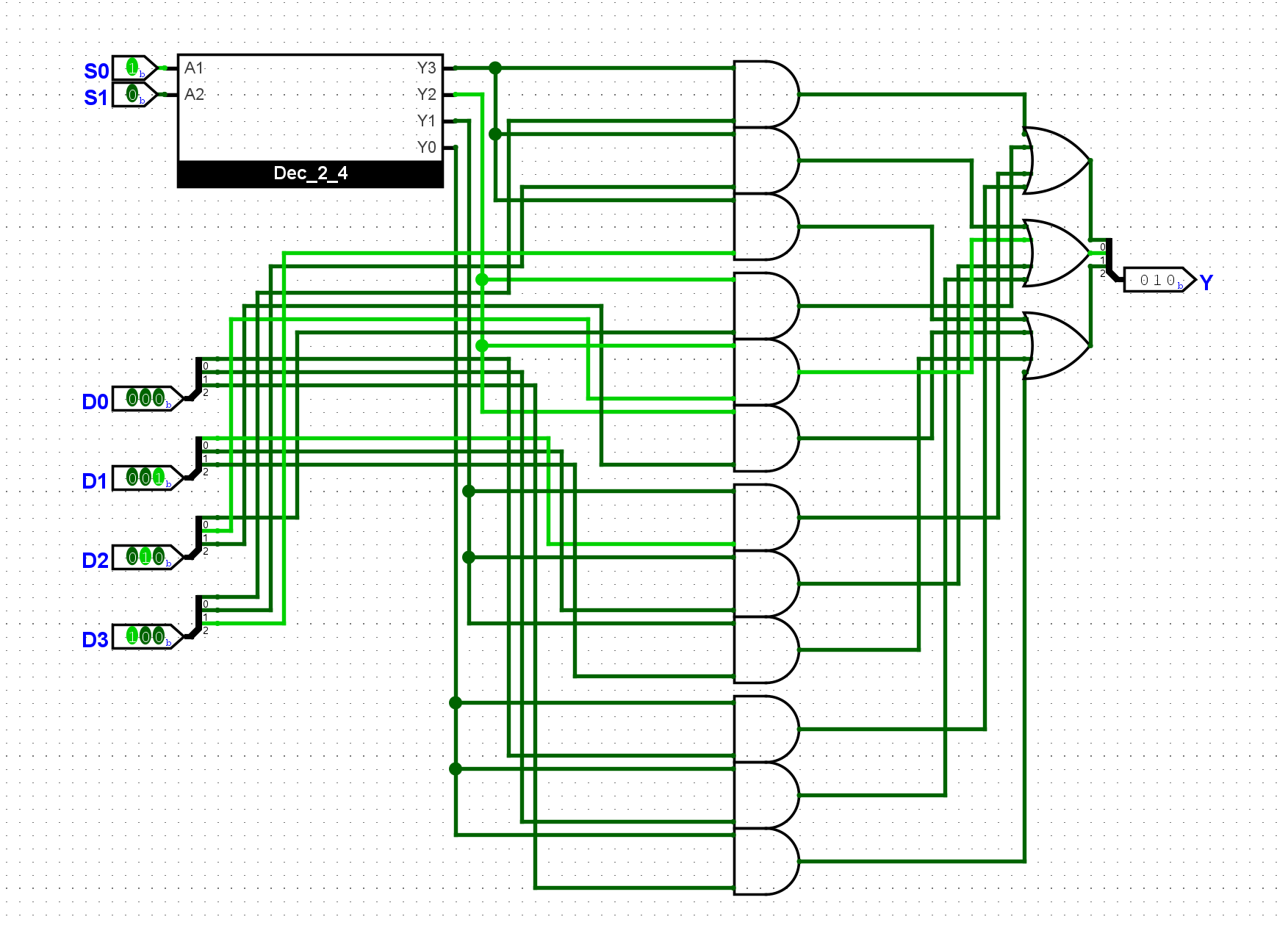

F3.5.11 搭建3位4选1选择器

尝试画出3位4选1选择器的电路结构图, 然后在Logisim中通过门电路搭建一个3位4选1选择器. 搭建后, 通过仿真检查你的方案是否正确.

这个比较复杂,但是原理一样:

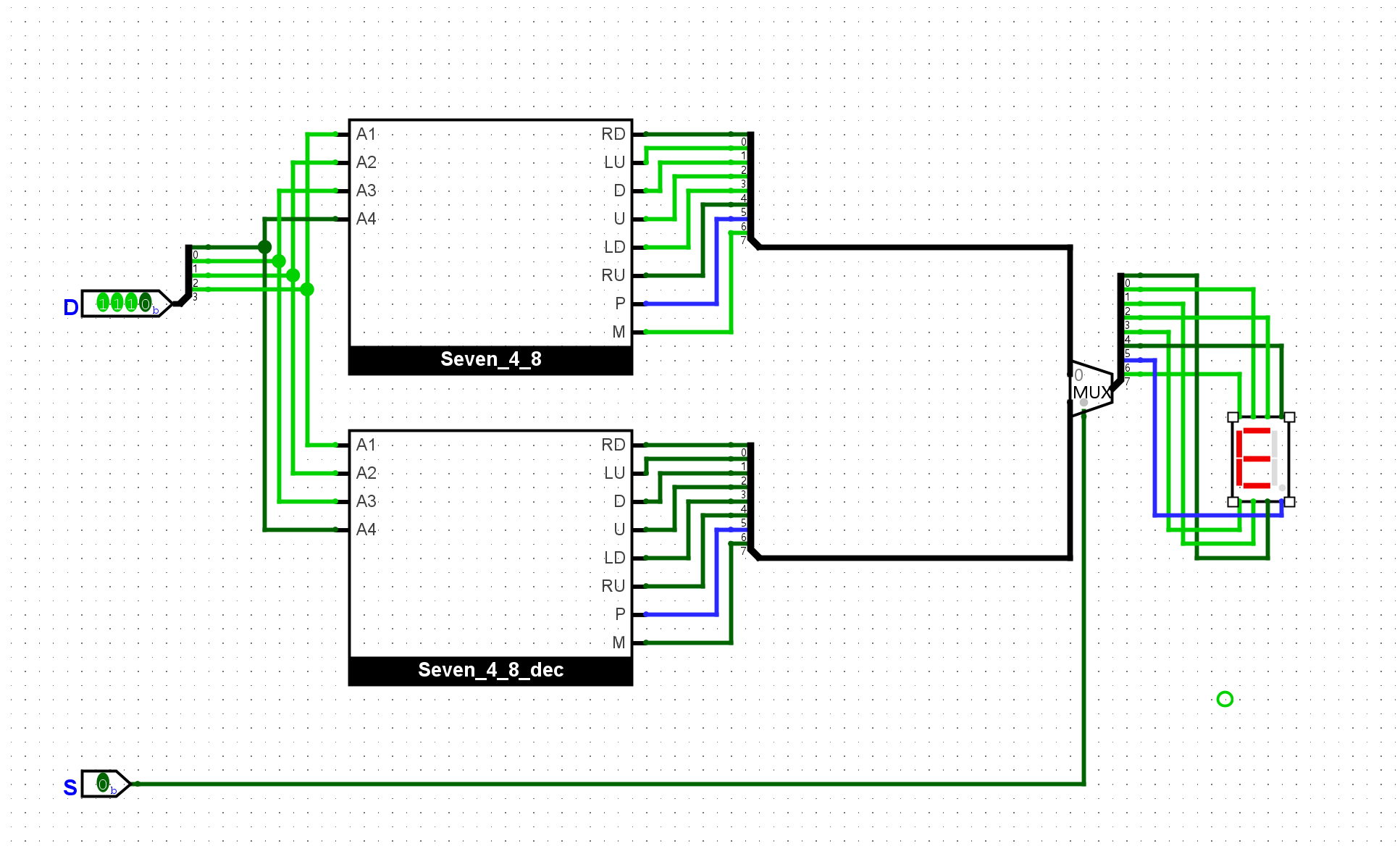

F3.5.12 搭建可切换进位计数制的七段数码管

通过5个拨码开关和1个七段数码管, 实现如下功能: 其中4个拨码开关当作数据输入, 剩下1个拨码开关作为进位计数制的选择, 当选择信号为

0时, 七段数码管以十进制方式显示数据; 当选择信号为1时, 七段数码管以十六进制方式显示数据. 在输入数据为10-15时, 两种显示方式有所不同.

使用系统封装好的多路复用器就很容易实现

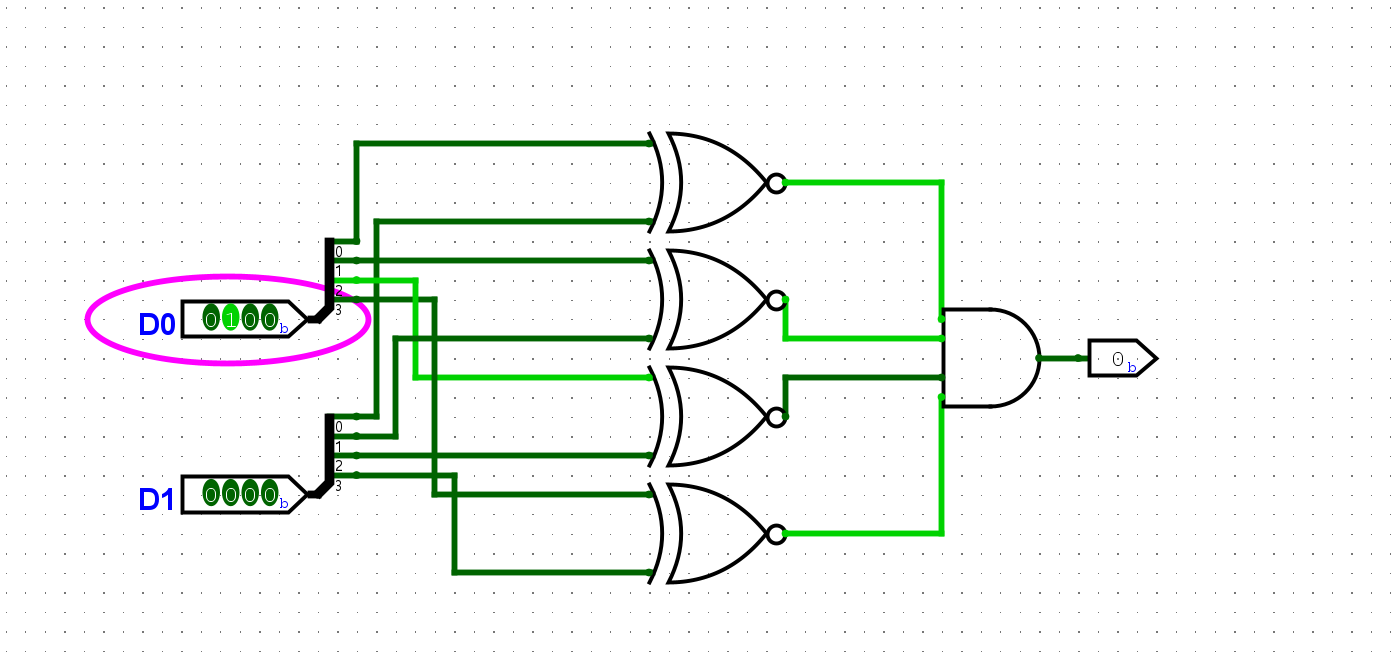

F3.5.13 搭建比较器

尝试在Logisim中通过门电路搭建一个4位比较器, 然后通过两组拨码开关对比两组数据是否相等, 若相等, 则点亮一个LED灯. 搭建后, 通过仿真检查你的方案是否正确.

四个同或门比较信号,然后使用与门收集信号,若全为真则各位相同:

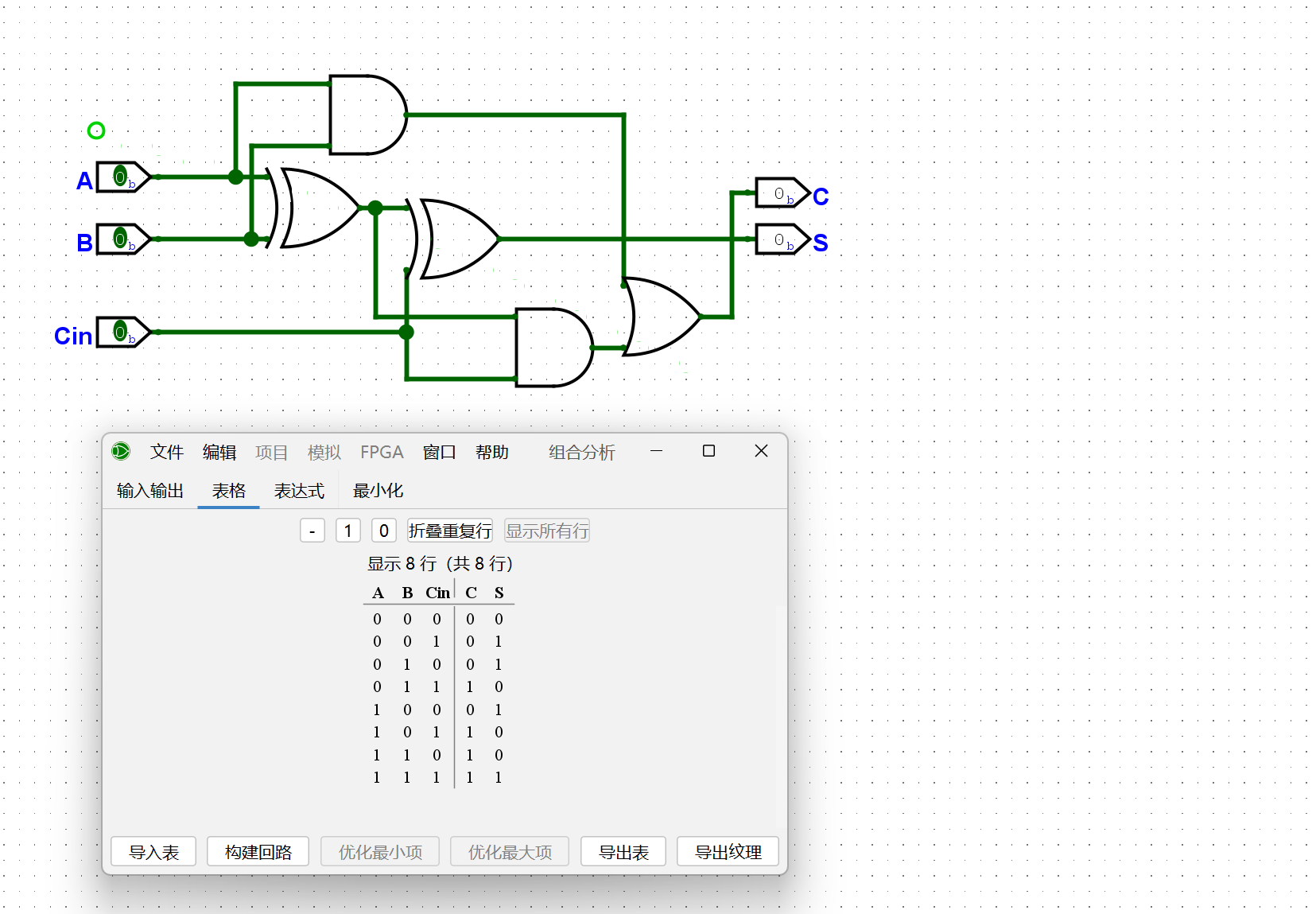

F3.5.14 搭建1位全加器

尝试列出1位全加器的真值表, 并在Logisim中通过门电路搭建一个1位全加器. 搭建后, 通过仿真检查你的方案是否正确.

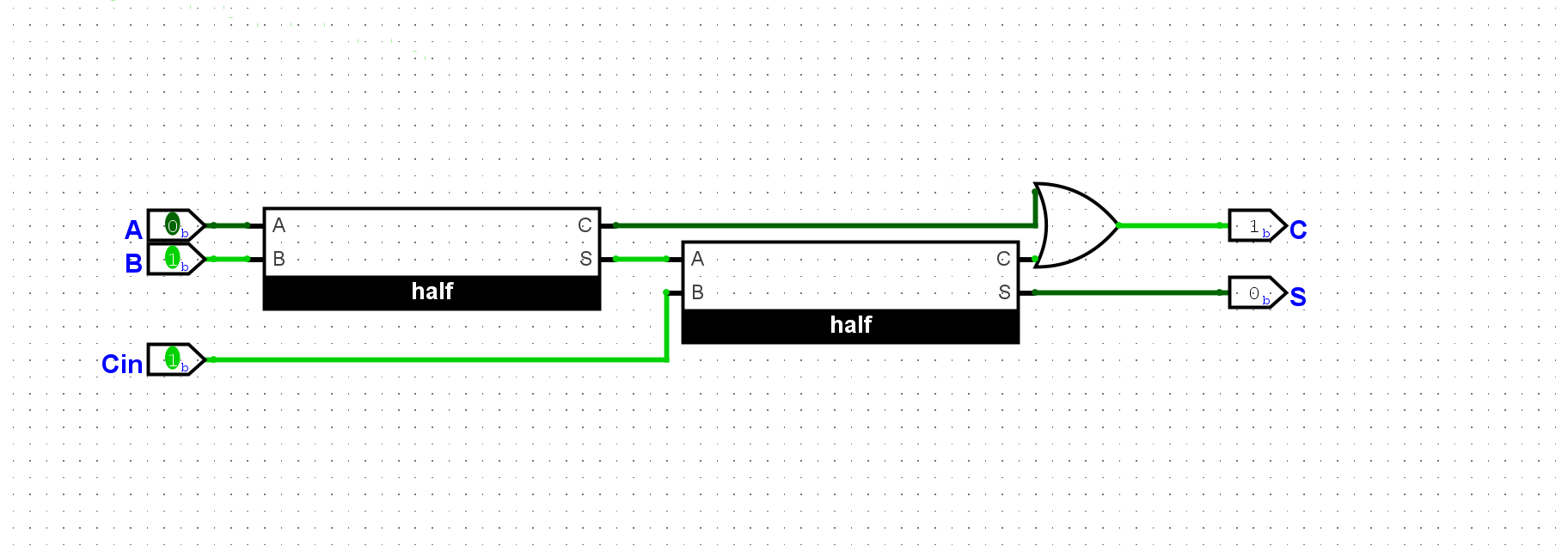

本质上就是在半加器的基础上,对一个新的进位进行额外的判断:

F3.5.15 搭建1位全加器(2)

尝试实例化若干个半加器, 并添加少量门电路, 从而实现一个1位全加器. 搭建后, 通过仿真检查你的方案是否正确.

一样的原理,只不过封装了起来

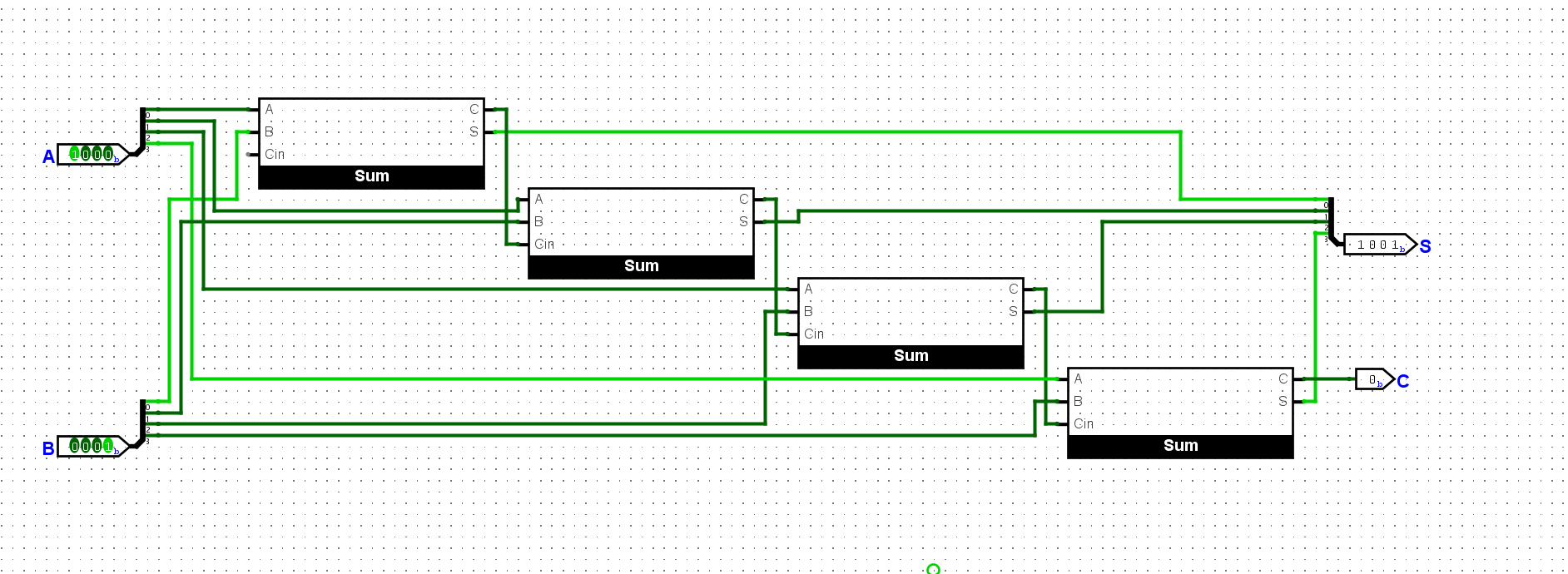

F3.5.16 搭建4位加法器

尝试在Logisim中通过门电路搭建一个4位加法器, 用七段数码管按十六进制显示加法器的两个输入和结果, 并用一个LED灯指示加法结果是否产生进位. 搭建后, 通过仿真检查你的方案是否正确.

使用全加器串联起来: